# Quality Control and Performance Evaluation of Cold Electronics for the DUNE Far Detector

NAM Hokyeong<sup>1</sup>, MASUD Mehedi<sup>1</sup>, and KIM Suhyeon<sup>1</sup> (1Department of Physics, Chung-Ang University)

#### Abstract

The Deep Underground Neutrino Experiment (DUNE) is a next-generation neutrino oscillation experiment designed to investigate fundamental properties of neutrinos. To achieve optimal performance, Cold Electronics (CE) has been chosen as the readout solution for the Far detector. These electronics must reliably operate at liquid argon (LAr) temperatures throughout the detector's expected lifetime of over 20 years, as maintenance or replacement will not be feasible. A comprehensive quality control (QC) procedure was implemented to ensure the electronics meet the specifications and the high quality-standards of DUNE, utilizing the DUNE ASIC Test (DAT), Robotic Test System (CTS). Three key components of the front-end readout system—COLDATA, the Front-End Motherboard (FEMB), and LArASIC—undergo rigorous QC procedures to assess their performance. We present a new selection criteria to identify high-quality components.

#### **DUNE Overview**

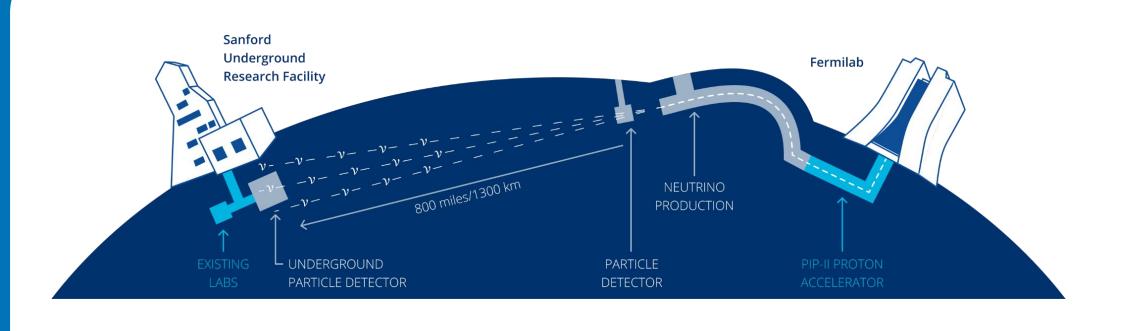

- **DUNE** is designed to study neutrino oscillations over a 1,300 km baseline from Fermilab to the Sanford Underground Research Facility

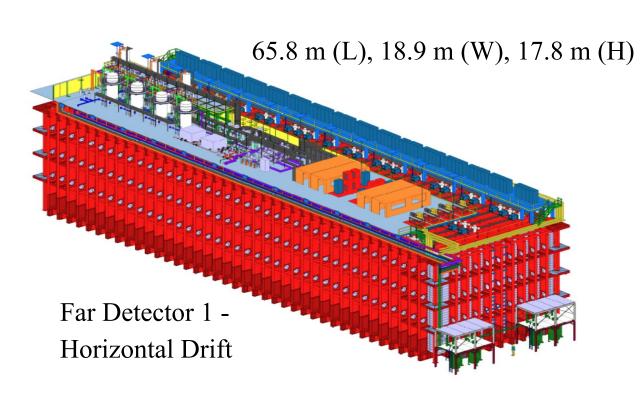

- The Far Detector comprises massive Liquid Argon Time Projection Chambers (LArTPCs), enabling precise 3D imaging of neutrino interactions

- Each module integrates advanced CE systems for signal amplification and digitization at cryogenic temperatures

#### **Cold Electronics**

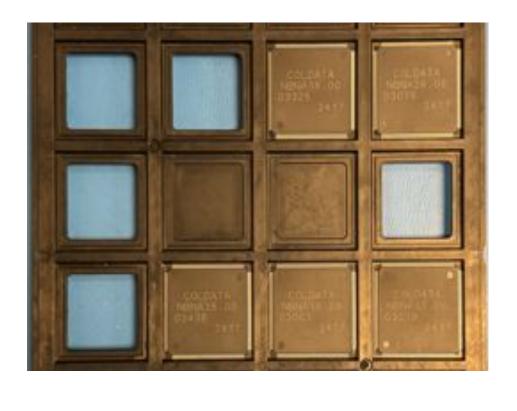

COLDATA

- COLDATA configures and controls 4 COLDADCs and 4 LArASICs

- LArASIC provides front-end amplification

- Four adjustable gain levels: 4.7, 7.8, 14, 25 mV/fC

- Front-End Motherboard (FEMB) integrates all ASICs:

- 8 x LArASIC, 8 x ColdADC, 2 x COLDATA

### **Quality Control & Test Setup**

Three QC test setups are implemented:

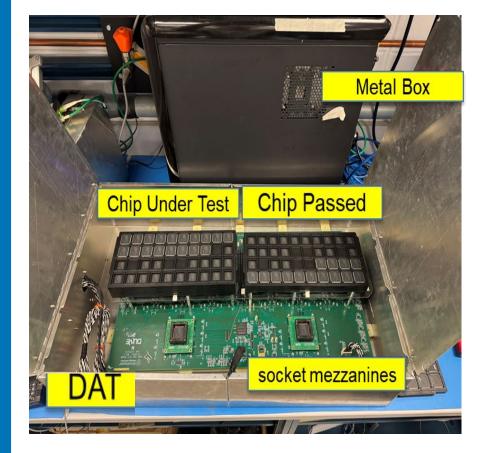

DAT (DUNE ASIC Test)

| COLDATA`                           | Qty    | Note                                        |

|------------------------------------|--------|---------------------------------------------|

| PASS                               | 159    | 86% yield                                   |

| Fail SPI communication with FE     | 3      |                                             |

| Handling issues                    | 2      | PASS QC after re-align                      |

| Poor contact between socket & chip | 2      | PASS after retest                           |

| Fail in EFUSE programmong          | 2      |                                             |

| PLL Band Range                     | 18     | PASS (17 chips) with new selection criteria |

| Total                              | PASSED | 176                                         |

|                                    | FAILED | 8                                           |

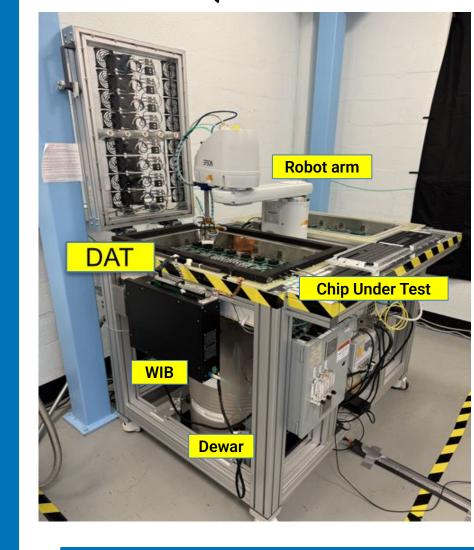

#### \* RTS (Robotic Testing Setup)

- Supports automated testing at both room temperature (RT) and Liquid Nitrogen temperature (LN)

- **Utilizes an EPSON robotic arm** to handle CE chips precisely and efficiently

- Enables repeatable, and scalable QC for high-volume testing

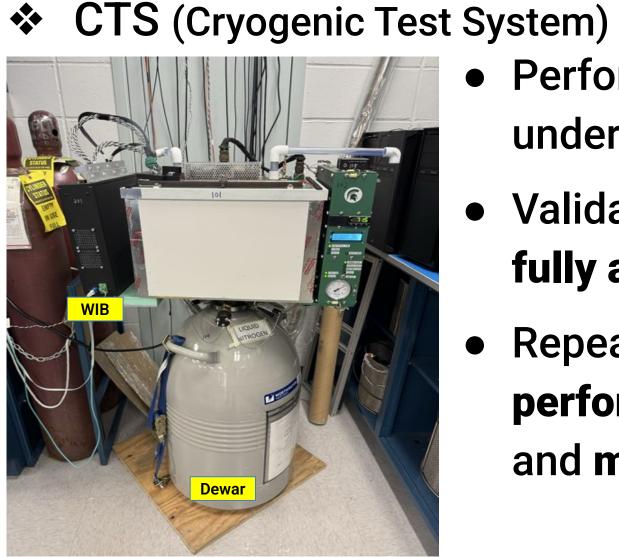

- Performs full-module testing under RT and LN conditions

- Validates cold operation as a fully assembled unit

- Repeated testing ensures performance consistency and mechanical endurance

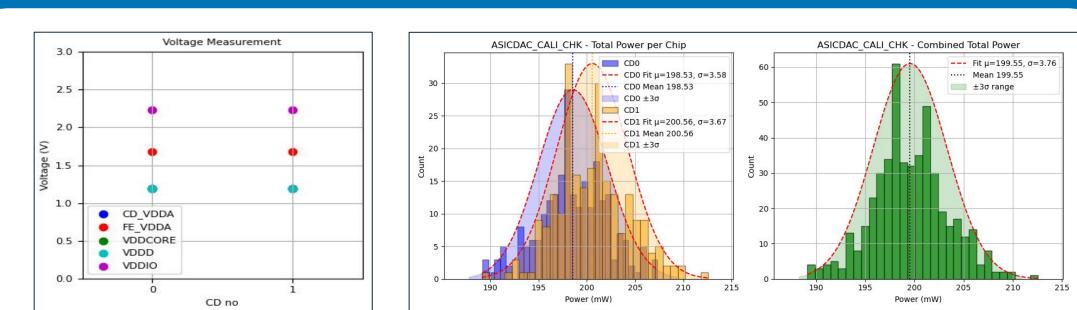

### Performance Evaluation from QC Data

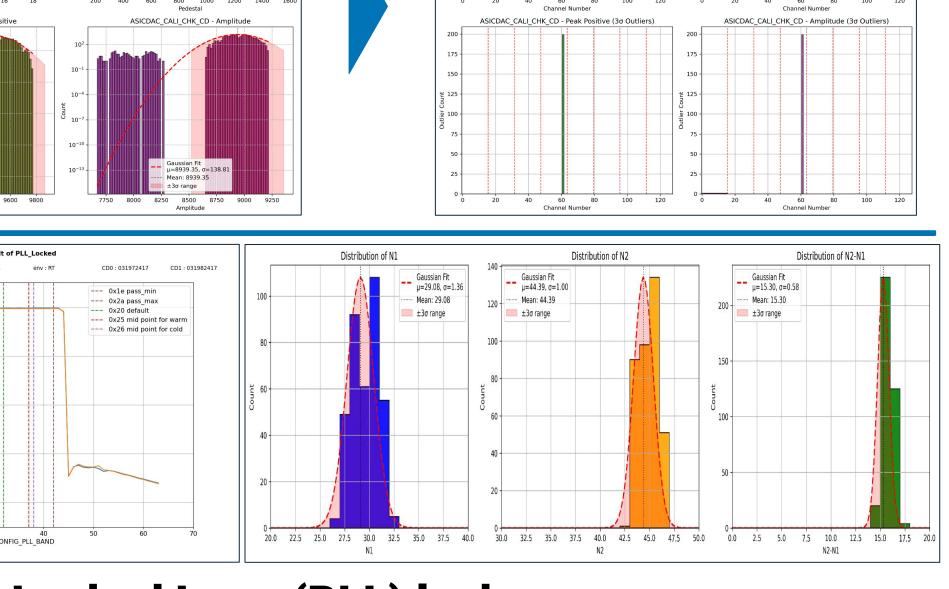

- Power consumption

- Meet the DUNE requirements: less than 50 mW

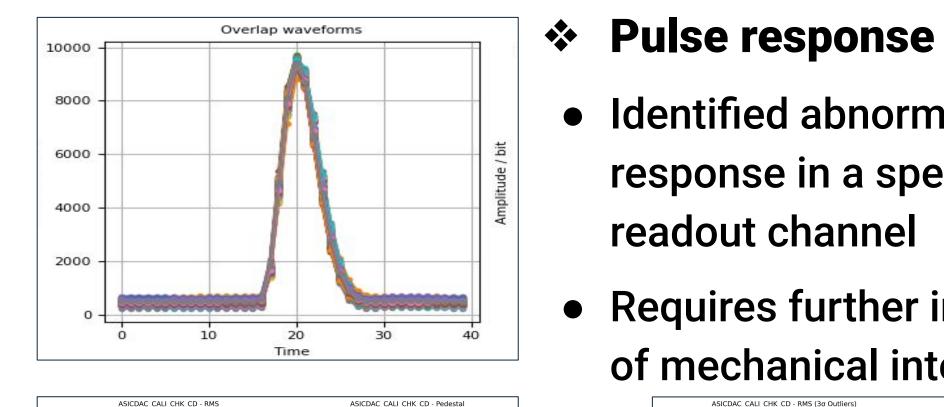

readout channel

Requires further inspection of mechanical integrity

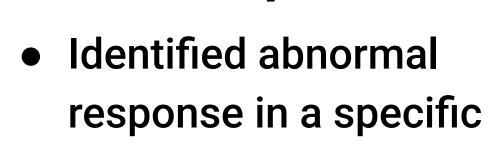

- Phase-Locked Loop (PLL) lock range

- 86% yield with conservative criteria

- 96% yield achieved with the updated criteria

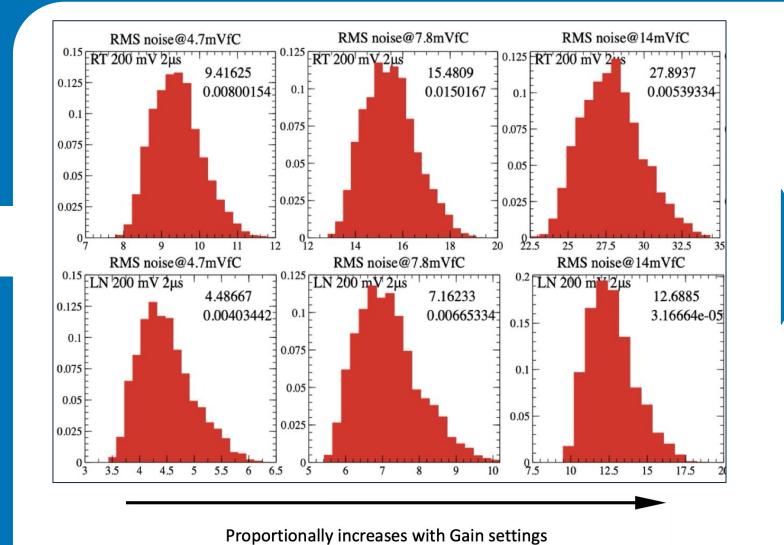

RMS noise

RT v.s LN

Power consumption RT v.s LN

- The average RMS noise decreases from 11.19 ADC to 7.17 ADC (36% reduction)  $\rightarrow$  lower than requirements (1000 ENC)

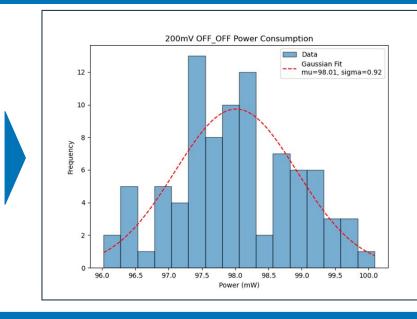

- Power consumption decreases from 98.01 mW to 92.65 mW (5.5% reduction)

- RMS noise (RT v.s LN)

- FEMB QC testing at various Gain settings

- Demonstrated stable performance under repeated thermal cycling between RT and LN

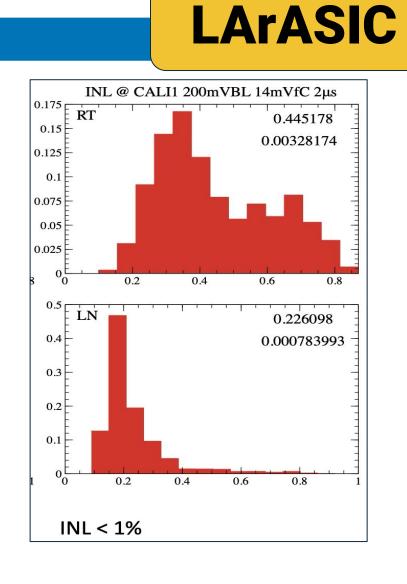

- Noise reduce by more than half at LN and integrated non-linearity < 1%

**FEMB**

## Conclusion

- > COLDATA analysis suggests a new chip selection criterion for future QC

- > LArASIC results demonstrate successful noise reduction at cryogenic temperature

- > FEMB testing validates the durability and reliability of the QC test setup

- > These results support the readiness of CE components and provide a foundation for future QC efforts across collaborating institutions

# Acknowledgement

**COLDATA**

- We thank the BNL Cold Electronics Group & CAU NuLa Group for this support and collaboration

- Special thanks to Shanshan Gao, Vladimir Tishchenko, Lingyun Ke for their invaluable guidance

- We also acknowledge the resource support provided by members of the CAU NuLa Group